ALC885_1-1

ALC885_1-1

6. 引脚描述

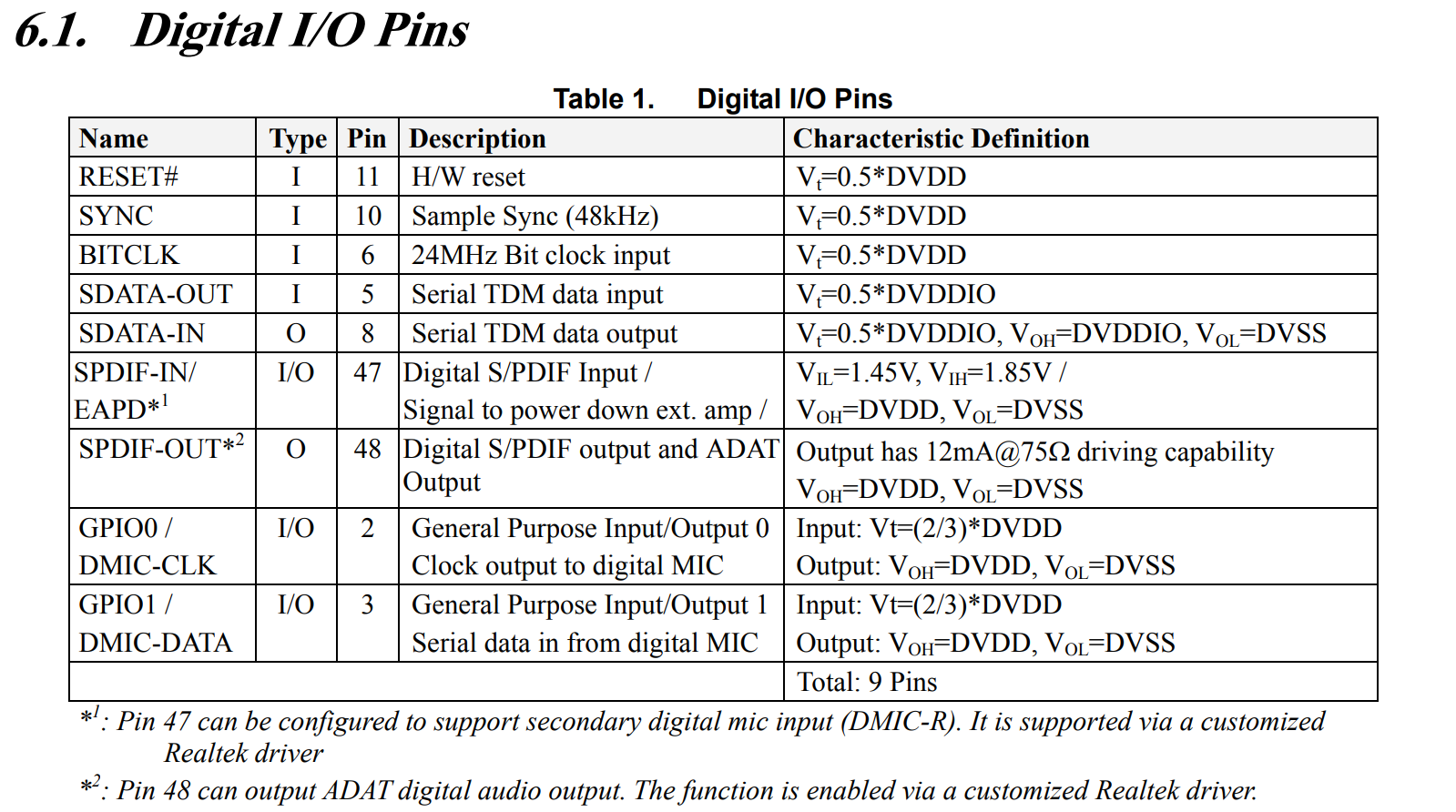

6.1 数字输入/输出

数字输入/输出(Digital I/O)引脚是处理数字信号的引脚,用于输入和输出数字数据。总计:9个引脚。以下是ALC885音频编解码器的数字输入/输出引脚的描述和特征定义:

RESET# (引脚类型: 输入, 引脚编号: 11):硬件复位信号,当为低电平时对芯片进行复位。特征定义为Vt=0.5*DVDD(即复位阈值为DVDD的一半)。

SYNC (引脚类型: 输入, 引脚编号: 11):采样同步信号,用于48kHz采样同步。特征定义为Vt=0.5*DVDD。

BITCLK (引脚类型: 输入, 引脚编号: 6):24MHz位时钟输入,用于同步数据传输。特征定义为Vt=0.5*DVDD。

SDATA-OUT (引脚类型: 输入, 引脚编号: 5):串行TDM(时分多路复用)数据输入,用于输入音频数据。特征定义为Vt=0.5*DVDDIO。

SDATA-IN (引脚类型: 输入, 引脚编号: 8):串行TDM数据输出,用于输出音频数据。特征定义为Vt=0.5*DVDDIO,VOH=DVDDIO(输出高电平为DVDDIO),VOL=DVSS(输出低电平为DVSS)。

SPDIF-IN / EAPD*1 (引脚类型: 输入/输出, 引脚编号: 47):数字S/PDIF输入,用于接收数字音频信号;也可以用于控制外部放大器的电源(EAPD)。特征定义为VIL=1.45V(输入低电平阈值为1.45V),VIH=1.85V(输入高电平阈值为1.85V),VOH=DVDD(输出高电平为DVDD),VOL=DVSS(输出低电平为DVSS)。

SPDIF-OUT*2 (引脚类型: 输入, 引脚编号: 48):数字S/PDIF输出和ADAT输出,用于输出数字音频信号,输出具有12mA @ 75Ω驱动能力。特征定义为VOH=DVDD(输出高电平为DVDD),VOL=DVSS(输出低电平为DVSS)。

GPIO0 / DMIC-CLK (引脚类型: 输入/输出, 引脚编号: 2):通用输入/输出引脚0,用于提供数字麦克风(DMIC)的时钟输出。输入时特征定义为Vt=(2/3)*DVDD,输出时特征定义为VOH=DVDD(输出高电平为DVDD),VOL=DVSS(输出低电平为DVSS)。

GPIO1 / DMIC-DATA (引脚类型: 输入/输出, 引脚编号: 3):通用输入/输出引脚1,用于提供从数字麦克风(DMIC)接收的串行数据输入。输入时特征定义为Vt=(2/3)*DVDD,输出时特征定义为VOH=DVDD(输出高电平为DVDD),VOL=DVSS(输出低电平为DVSS)。

*1:引脚47可配置为支持辅助数字麦克风输入(DMIC-R),通过定制的Realtek驱动支持。

*2:引脚48可以输出ADAT数字音频输出,该功能通过定制的Realtek驱动启用。

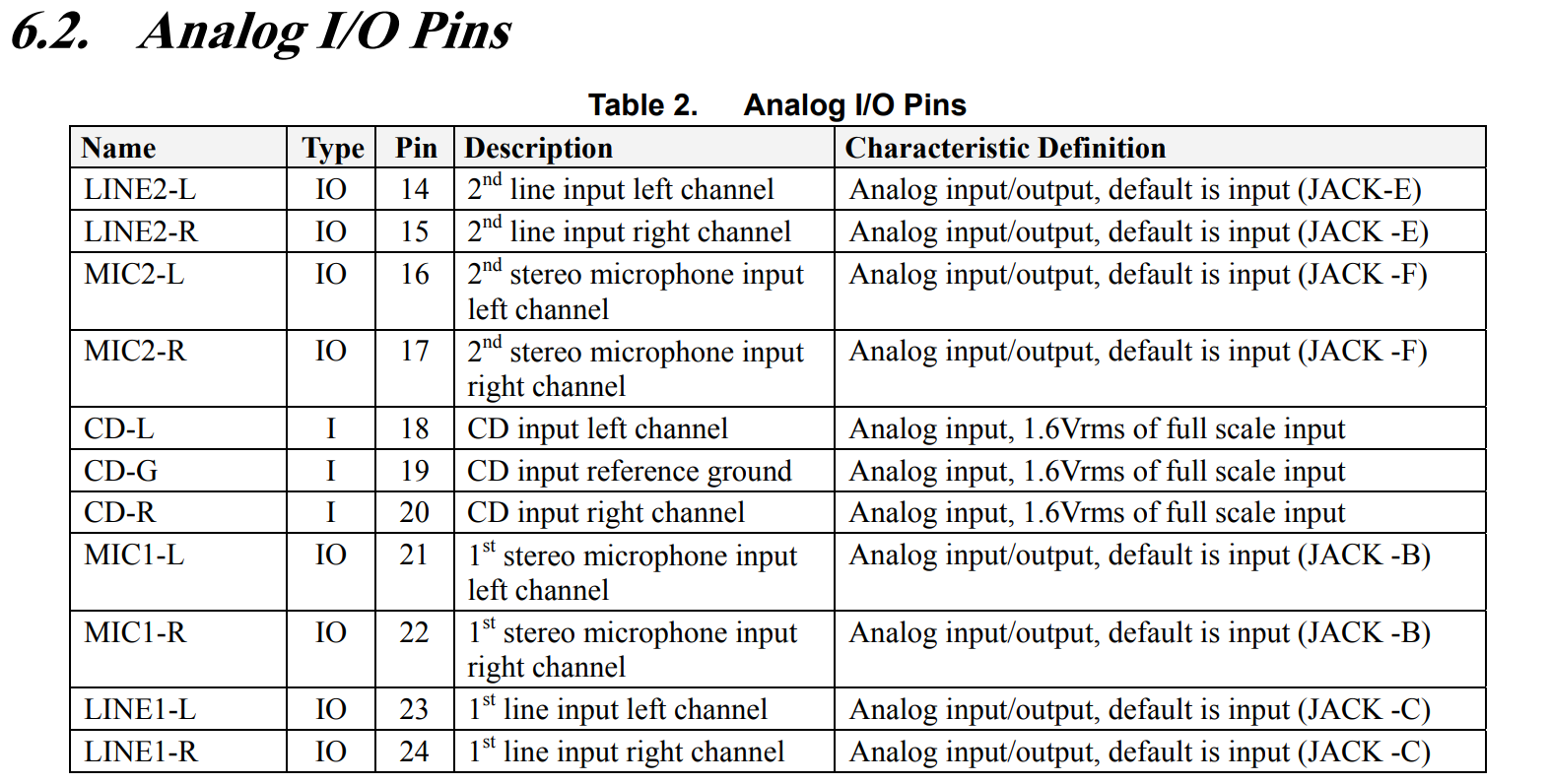

6.2 数字输入/输出

上述是ALC885音频编解码器的模拟I/O引脚描述,总共有22个引脚,这些引脚用于连接到各种音频输入设备和输出设备,以实现高性能的音频处理和播放功能:

LINE2-L (引脚类型: 输入/输出, 引脚编号: 14): 第二线输入左声道。模拟输入/输出,默认为输入模式。通常用于连接第二条线输入设备。(标识为JACK-E)

LINE2-R (引脚类型: 输入/输出, 引脚编号: 15): 第二线输入右声道。模拟输入/输出,默认为输入模式。通常用于连接第二条线输入设备。(标识为JACK-E)

MIC2-L (引脚类型: 输入/输出, 引脚编号: 16): 第二个立体声麦克风输入左声道。模拟输入/输出,默认为输入模式。通常用于连接第二个立体声麦克风。(标识为JACK-F)

MIC2-R (引脚类型: 输入/输出, 引脚编号: 17): 第二个立体声麦克风输入右声道。模拟输入/输出,默认为输入模式。通常用于连接第二个立体声麦克风。(标识为JACK-F)

CD-L (引脚类型: 输入, 引脚编号: 18): CD输入左声道。模拟输入,最大电压为1.6Vrms。(标识为JACK-G)

CD-G (引脚类型: 输入, 引脚编号: 19): CD输入参考地。模拟输入,最大电压为1.6Vrms。(标识为JACK-G)

CD-R (引脚类型: 输入, 引脚编号: 20): CD输入右声道。模拟输入,最大电压为1.6Vrms。(标识为JACK-G)

MIC1-L (引脚类型: 输入/输出, 引脚编号: 21): 第一个立体声麦克风输入左声道。模拟输入/输出,默认为输入模式。通常用于连接第一个立体声麦克风。(标识为JACK-B)

MIC1-R (引脚类型: 输入/输出, 引脚编号: 22): 第一个立体声麦克风输入右声道。模拟输入/输出,默认为输入模式。通常用于连接第一个立体声麦克风。(标识为JACK-B)

LINE1-L (引脚类型: 输入/输出, 引脚编号: 23): 第一线输入左声道。模拟输入/输出,默认为输入模式。通常用于连接第一条线输入设备。(标识为JACK-C)

LINE1-R (引脚类型: 输入/输出, 引脚编号: 24): 第一线输入右声道。模拟输入/输出,默认为输入模式。通常用于连接第一条线输入设备。(标识为JACK-C)

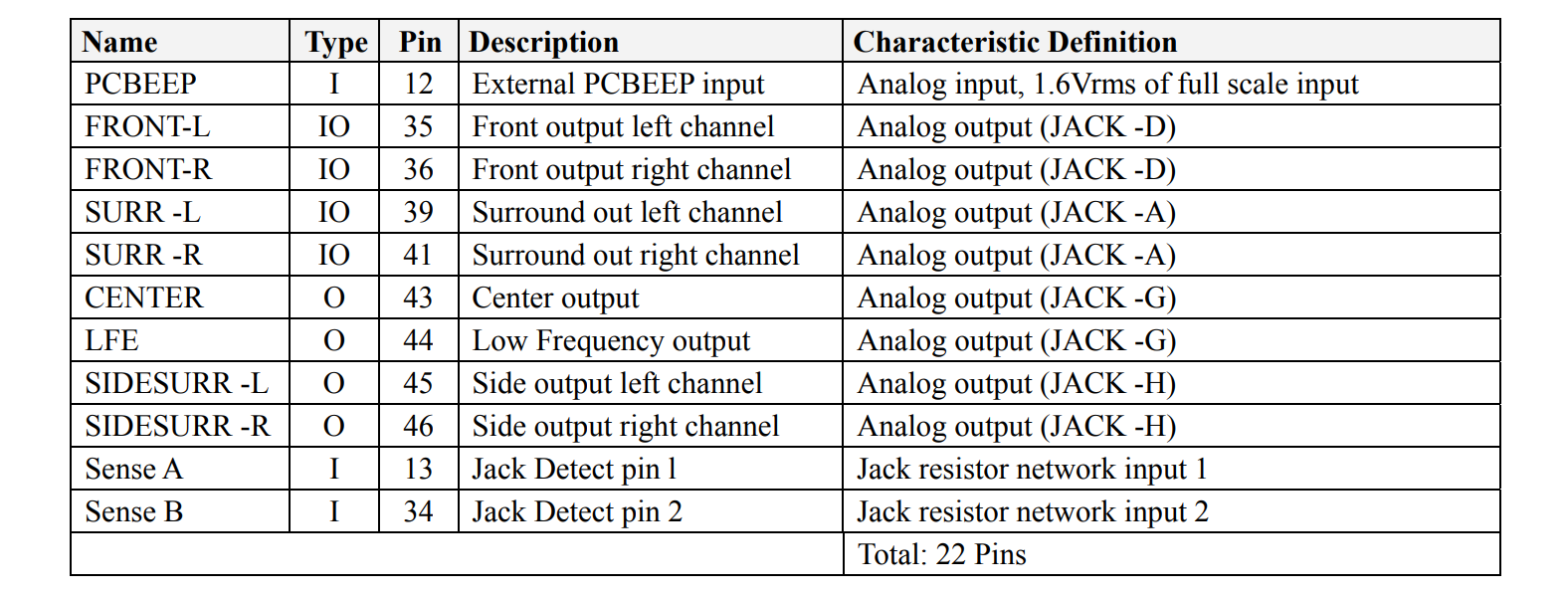

PCBEEP (引脚类型: 输入, 引脚编号: 12): 外部PCBEEP输入。模拟输入,最大电压为1.6Vrms的满量程输入。

FRONT-L (引脚类型: 输入/输出, 引脚编号: 35): 前置输出左声道。模拟输出,用于连接前置输出设备。(标识为JACK-D)

FRONT-R (引脚类型: 输入/输出, 引脚编号: 36): 前置输出右声道。模拟输出,用于连接前置输出设备。(标识为JACK-D)

SURR -L (引脚类型: 输入/输出, 引脚编号: 39): 环绕声输出左声道。模拟输出,用于连接环绕声输出设备。(标识为JACK-A)

SURR -R (引脚类型: 输入/输出, 引脚编号: 41): 环绕声输出右声道。模拟输出,用于连接环绕声输出设备。(标识为JACK-A)

CENTER (引脚类型: 输出, 引脚编号: 43): 中央输出。模拟输出,用于连接中央输出设备。(标识为JACK-G)

LFE (引脚类型: 输出, 引脚编号: 44): 低频输出。模拟输出,用于连接低频输出设备。(标识为JACK-G)

SIDESURR -L (引脚类型: 输出, 引脚编号: 45): 侧面环绕声输出左声道。模拟输出,用于连接侧面环绕声输出设备。(标识为JACK-H)

SIDESURR -R (引脚类型: 输出, 引脚编号: 46): 侧面环绕声输出右声道。模拟输出,用于连接侧面环绕声输出设备。(标识为JACK-H)

Sense A (引脚类型: 输入, 引脚编号: 13): 插孔检测引脚A。用于连接插孔电阻网络输入1。

Sense B (引脚类型: 输入, 引脚编号: 34): 插孔检测引脚B。用于连接插孔电阻网络输入2。

6.3 Filter/Reference/NC

这里是Filter/Reference引脚的详细描述,总共有8个引脚,这些引脚用于提供偏置电压和参考电压,以支持插孔检测和其他音频功能:

VREF (引脚类型: 输出, 引脚编号: 27): 2.5V参考电压。连接10uF电容到模拟地。

MIC1-VREFO-L (引脚类型: 输出, 引脚编号: 28): MIC1插孔左声道偏置电压。2.5V/3.75V参考电压。

LINE1-VREFO (引脚类型: 输出, 引脚编号: 29): LINE1插孔偏置电压。2.5V/3.75V参考电压。

MIC2-VREFO (引脚类型: 输出, 引脚编号: 30): MIC2插孔偏置电压。2.5V/3.75V参考电压。

LINE2-VREFO (引脚类型: 输出, 引脚编号: 31): LINE2插孔偏置电压。2.5V/3.75V参考电压。

MIC1-VREFO-R (引脚类型: 输出, 引脚编号: 32): MIC1插孔右声道偏置电压。2.5V/3.75V参考电压。

NC (引脚类型: 不连接, 引脚编号: 37): 未连接。

JDREF (引脚类型: 输出, 引脚编号: 40): 插孔检测的参考电阻。连接到20K, 1%的外部电阻和模拟地。

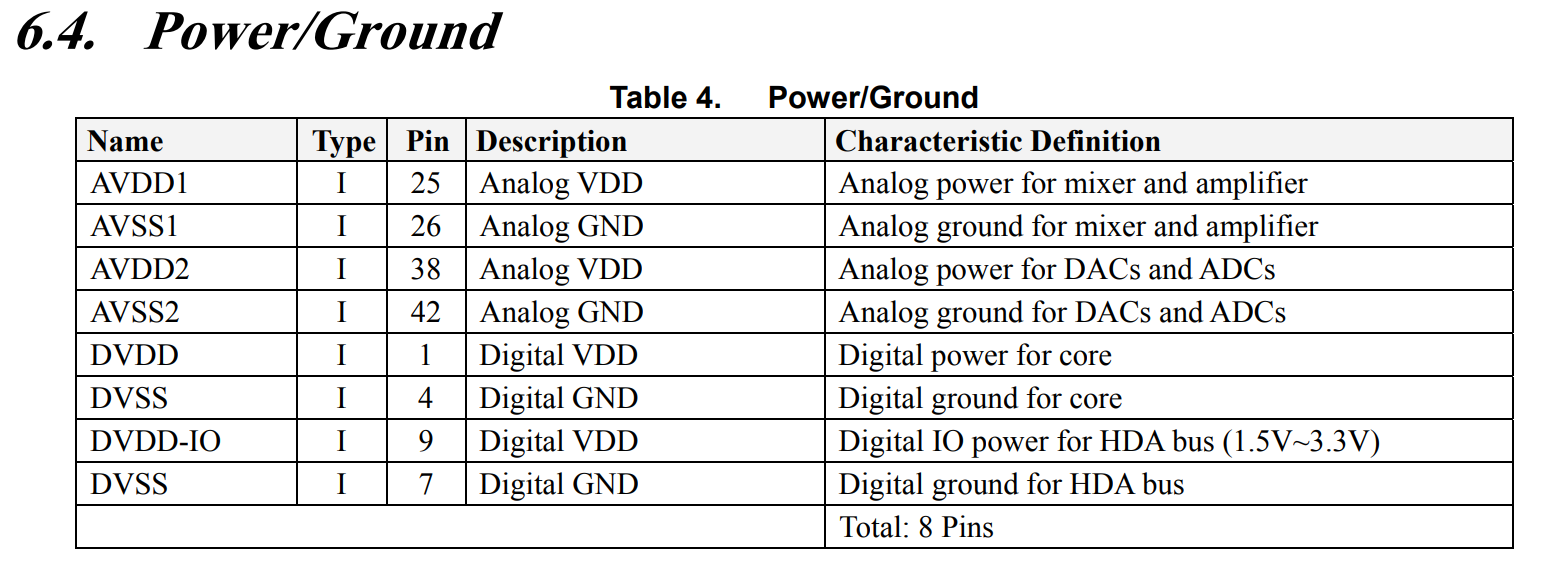

6.4 Power/Ground

这些引脚用于为IC的不同部分提供所需的电源和地线。总共有8个引脚,AVDD是用于模拟电路的电源,而DVDD用于数字核心和HDA总线。

AVDD1 (引脚类型: 输入,引脚编号: 25): 模拟电源供应,用于混音器和放大器的模拟电路。

AVSS1 (引脚类型: 输入,引脚编号: 26): 模拟地,用于混音器和放大器的模拟电路。

AVDD2 (引脚类型: 输入,引脚编号: 38): 模拟电源供应,用于DAC和ADC的模拟电路。

AVSS2 (引脚类型: 输入,引脚编号: 42): 模拟地,用于DAC和ADC的模拟电路。

DVDD (引脚类型: 输入,引脚编号: 1): 数字核心的数字电源供应。

DVSS (引脚类型: 输入,引脚编号: 4, 7): 数字核心的数字地,同时也是HDA总线的数字地。

DVDD-IO (引脚类型: 输入,引脚编号: 9): HDA总线的数字IO电源,电压范围为1.5V~3.3V。

7. HDA链路协议

7.1. 链路信号

高清晰度音频(High Definition Audio,HDA)链路是连接HDA编解码器与HDA控制器的数字串行接口。HDA链路协议是控制器同步的,基于由HDA控制器发送的24.0MHz BIT-CLK(位时钟)。输入和输出流,包括命令和PCM数据,与48kHz帧率同步。图4展示了HDA链路协议的基本概念。

在HDA链路中,HDA控制器负责控制通信的时序,并通过BIT-CLK来同步数据传输。PCM数据是指脉冲编码调制(Pulse Code Modulation)的音频数据,用于音频的录制和播放。所有数据在HDA链路中按照特定的帧率进行传输,这样可以确保音频数据的准确性和同步。

链路中的输入和输出数据流称为isochronous流,这意味着数据传输是基于相同的时钟,保持相等的时间间隔,从而实现实时的音频传输。这种isochronous传输方式非常重要,因为它确保了音频数据的连续性和一致性,避免了音频播放过程中的间断和数据损失。

总体而言,HDA链路协议为HDA编解码器和HDA控制器之间的数据传输提供了可靠的时序和同步机制,确保高质量的音频传输和播放体验。

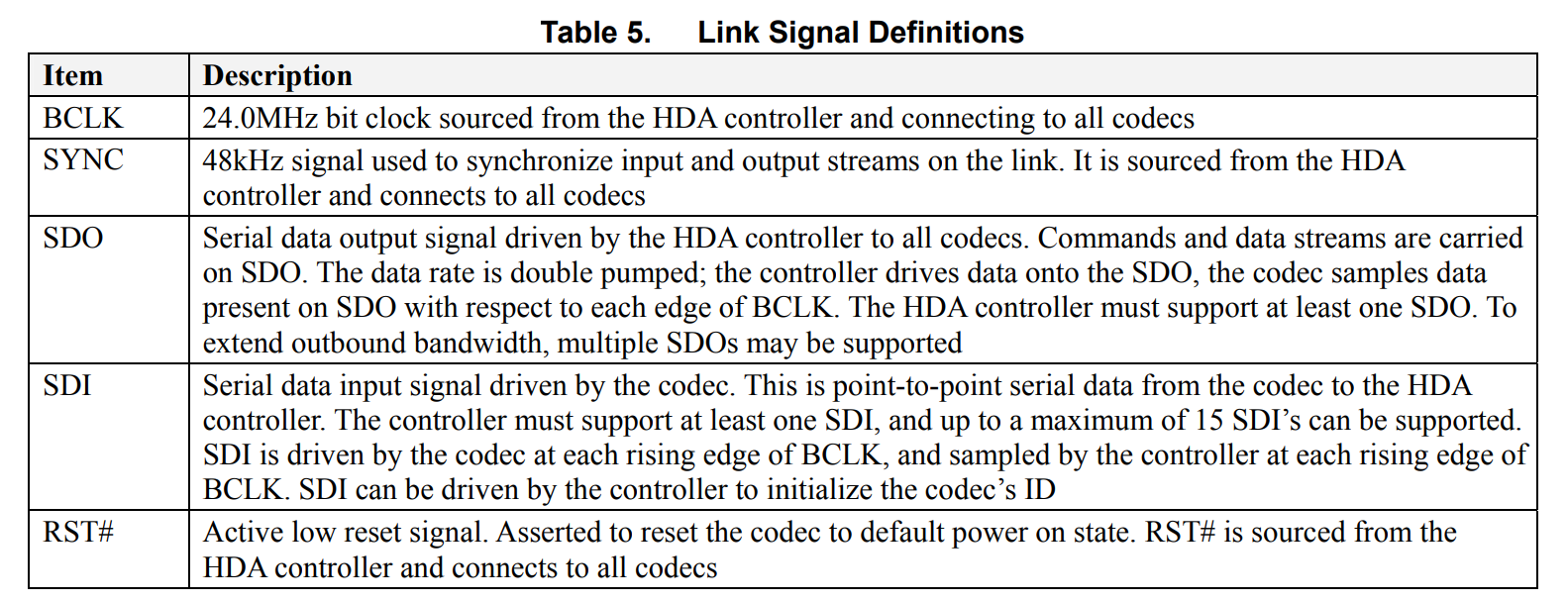

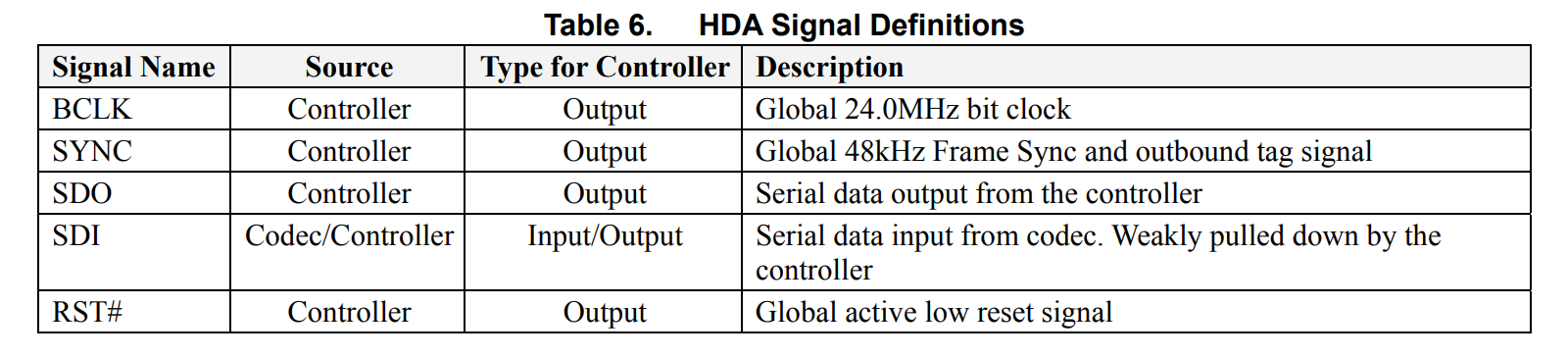

7.1.1. 链路信号定义

BCLK(位时钟):24.0MHz位时钟由HDA控制器提供,连接所有编解码器。BCLK用于同步数据传输和控制时序。

SYNC(同步信号):48kHz同步信号用于同步链路上的输入和输出流。它由HDA控制器提供,连接所有编解码器。

SDO(串行数据输出):SDO是由HDA控制器向所有编解码器驱动的串行数据输出信号。SDO上携带命令和数据流。数据速率是双泵送的,控制器将数据驱动到SDO上,编解码器会在每个BCLK上升沿时对SDO上的数据进行采样。HDA控制器必须支持至少一个SDO。为了扩展输出带宽,可以支持多个SDO。

SDI(串行数据输入):SDI是由编解码器驱动的点对点串行数据输入信号,用于从编解码器传输数据到HDA控制器。HDA控制器必须支持至少一个SDI,最多可以支持15个SDI。SDI由编解码器在每个BCLK上升沿时驱动,HDA控制器在每个BCLK上升沿时对SDI进行采样。HDA控制器可以驱动SDI以初始化编解码器的ID。

RST#(复位信号):RST#是低有效的复位信号,用于将编解码器重置到默认上电状态。RST#由HDA控制器提供,连接所有编解码器。当RST#被触发时,编解码器会返回到默认的初始状态。

| 信号名称 | 来源 | 控制器的类型 | 描述 | |

|---|---|---|---|---|

| BCLK | 控制器输出 | 全局 | 24.0MHz位时钟 | |

| SYNC | 控制器输出 | 全局 | 48kHz帧同步和出站标签信号 | |

| SDO | 控制器输出 | 串行 | 控制器的串行数据输出 | |

| SDI | 编解码器/控制器 | 输入/输出 | 编解码器传输给控制器的串行数据输入。由控制器弱上拉。 | |

| RST# | 控制器输出 | 全局 | 全局低有效的复位信号 |

7.1.2. 信号拓扑

HDA控制器支持两个SDO用于出站数据流,最多支持15个SDI用于入站数据流。RST#、BCLK、SYNC、SDO0和SDO1由控制器驱动到编解码器。每个编解码器驱动自己的点对点SDI信号到控制器。

图6显示了HDA控制器和编解码器之间的可能连接方式:

- • Codec 0是基本连接。有一个单一的SDO和一个单一的SDI用于正常传输。

- • Codec 1有两个SDO,用于加倍的出站速率,一个单一的SDI用于正常的入站速率。

- • Codec 3支持一个单一的SDO,用于正常的出站速率,以及两个SDI,用于加倍的入站速率。

- • Codec N有两个SDO和多个SDI。

多个SDO和多个SDI用于扩展控制器和编解码器之间的传输速率。第7.2节《帧构成》详细描述了单个和多个SDO/SDI的出站和入站数据流构成。

图6中显示的连接方式可以在HDA系统中同时实现。ALC885被设计为接收单一SDO流。

7.2. 帧构成

7.2.1. 出站帧 - 单一SDO

一个出站帧由一个32位的命令流和多个数据流组成。数据流中有一个或多个采样块。如果HDA控制器向编解码器传送48kHz的采样率,则一个流中只有一个采样块。而多个采样块意味着采样率是48kHz的倍数。这意味着在同一个流中应该有两个块来携带96kHz的采样(见图7)。 对于出站帧,流标签不在SDO中,而是在SYNC信号中。在流标签的末尾开始新的数据流。流标签包括一个4位的前导码和4位的流ID(见图8)。 为了保持绑定到同一数据流的转换器的节奏,这些转换器的采样必须放置在同一个块中。

7.2.2. 出站帧 - 多个SDO

HDA控制器允许使用两个SDO信号来进行出站数据的传输,从而在更短的时间内完成传输以获得更大的带宽。如果软件确定目标编解码器支持多个SDO功能,它会在控制器的输出流控制寄存器中启用"Stripe Control"位,以启动在多个SDO上传输特定的流(如图9中的流"A")。在这种情况下,数据流的最高有效位(MSB)总是携带在SDO0上,第二位携带在SDO1上,依此类推。 SDO1用于传输条带化的流。编解码器不支持多个SDO连接到SDO0。 为确保所有编解码器都可以确定其对应的数据流,命令流不进行分割。它总是在SDO0上传输,并且在SDO1上进行复制。

7.2.3. 入站帧 - 单个SDI

在HDA音频协议中,入站帧使用单个SDI(Serial Data Input)信号传输。入站帧由两个部分组成:响应流(response stream)和多个数据流。SDI信号由编解码器在每个BCLK(Bit Clock)上升沿处进行驱动。BCLK是HDA控制器提供的24.0MHz的比特时钟信号。

入站帧中的数据流标签(stream tag)不通过SYNC信号传输,而是包含在SDI信号中。一个完整的SDI数据流包括一个4位的流标签、一个6位的数据长度字段以及n位的采样块(sample blocks)。数据长度字段指示了数据流中的采样块长度,采样块可以是1个或多个采样点的组合。

需要注意的是,入站帧中的数据流标签和数据长度字段是按照特定的格式组织的,HDA控制器在每个BCLK上升沿处对这些字段进行采样,以正确解析接收到的数据。

7.2.4. 入站帧 - 多个SDI

HDA音频协议允许编解码器通过多个SDI信号向控制器传输数据,以实现更高的带宽。如果一个入站数据流超过了单个SDI的数据传输限制,编解码器可以将数据分成独立的多个SDI信号,每个信号在同一个帧时间内使用不同的流编号。这类似于将多个编解码器连接到控制器上。控制器通过多个DMA描述符将分开的数据流采样到独立的内存中,然后由软件将分开的数据重新组合成有意义的数据流。这样就可以通过多个SDI信号同时传输更大量的数据。

通过使用多个SDI信号,编解码器可以将一个大的数据流拆分成多个较小的数据流,从而充分利用系统带宽,提高音频数据传输的效率和速度。这在高质量音频传输和处理方面非常有用,特别是对于需要处理大量音频数据的应用场景。

7.2.5. 可变采样率

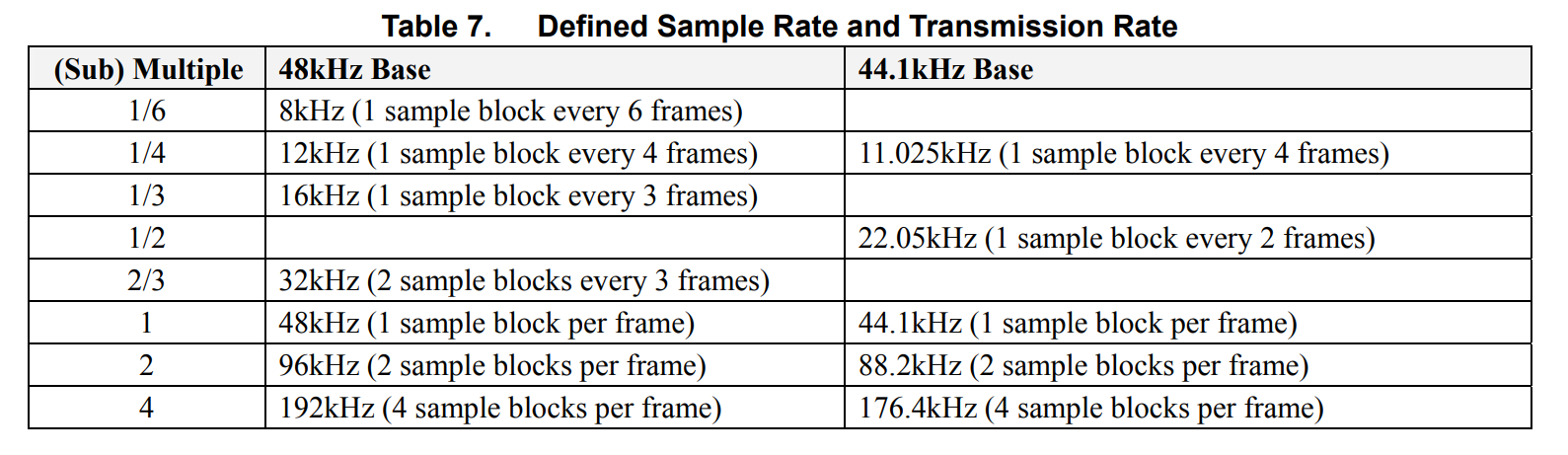

HDA链接设计用于48kHz的采样率。可变采样率以48kHz的倍数或子倍数的形式进行传递。每个帧中的两个采样块导致96kHz的传送速率,而每两个帧中的一个采样块导致24kHz的传送速率。HDA规范规定,出站流的采样率由控制器同步,而不是由编解码器同步。每个流都有自己的采样率,独立于任何其他流。

HDA控制器支持48kHz和44.1kHz的基本采样率。表7显示了基于这两个基本采样率的倍数或子倍数的推荐采样率。

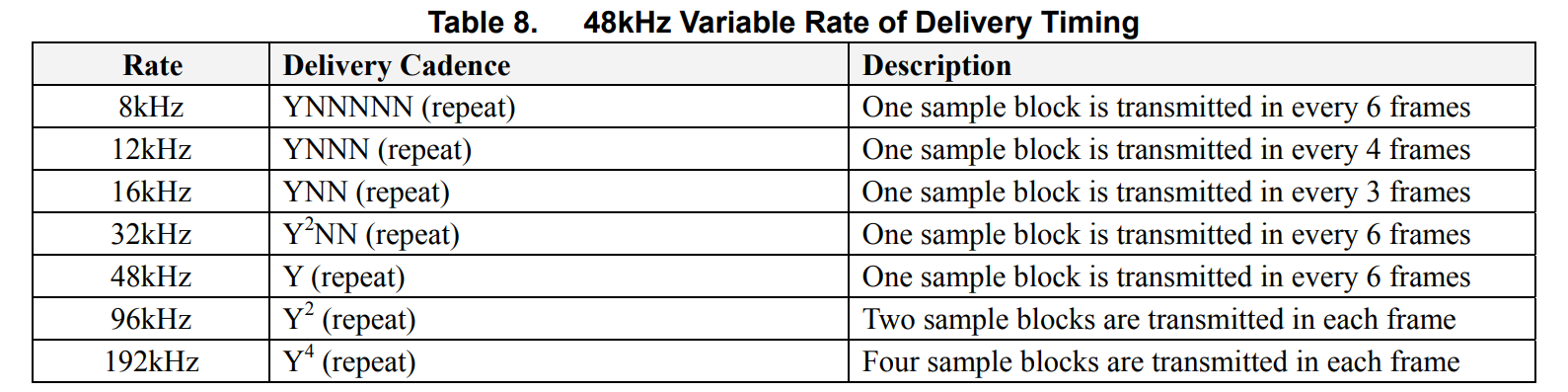

48kHz的子倍数采样率(1/n)包含n帧,其中不含任何采样块。48kHz的倍数采样率(n)在一个帧中包含n个采样块。表8显示了基于48kHz的可变采样率的传送节奏。

HDA链接被定义为以固定的48kHz帧率运行。要以(子)多个44.1kHz的采样率传送样本,必须维护44.1kHz和48kHz之间的适当比例,以避免频率漂移。44.1kHz和48kHz之间的适当比例是147/160,即每160帧传输147个采样块。采样节奏“12-11-11-12-11-11-12-11-11-12-11-11-11-(重复)”在每160帧中交错插入13个不含采样块的帧。这为44.1kHz的传送速率提供了低的长期频率漂移。44.1kHz的子倍数采样率也遵循此节奏,并在每个帧中交错插入n个空帧。44.1kHz的倍数采样率使用此节奏,在非空帧中包含n个采样块,并在非空帧之间交错插入一个空帧(见表9)。

- (子)多个 48kHz基准 44.1kHz基准

- 1/6 8kHz(每6帧1个采样块)

- 1/4 12kHz(每4帧1个采样块) 11.025kHz(每4帧1个采样块)

- 1/3 16kHz(每3帧1个采样块)

- 1/2 22.05kHz(每2帧1个采样块)

- 2/3 32kHz(每3帧2个采样块)

- 1 48kHz(每帧1个采样块) 44.1kHz(每帧1个采样块)

- 2 96kHz(每帧2个采样块) 88.2kHz(每帧2个采样块)

- 4 192kHz(每帧4个采样块) 176.4kHz(每帧4个采样块)

- 速率 传递时序 描述

- 8kHz YNNNNN (重复) 每6帧传输1个采样块

- 12kHz YNNN (重复) 每4帧传输1个采样块

- 16kHz YNN (重复) 每3帧传输1个采样块

- 32kHz Y2NN (重复) 每6帧传输1个采样块

- 48kHz Y (重复) 每帧传输1个采样块

- 96kHz Y2 (重复) 每帧传输2个采样块

- 192kHz Y4 (重复) 每帧传输4个采样块

note:

- N:帧中没有采样块

- Y:帧中有一个采样块

- Yx:帧中有X个采样块

这些符号代表了传输时每帧中采样块的情况。例如,YNNNNN表示每6帧中有一个采样块。

7.3. 复位和初始化

在HDA链路中,有两种类型的复位:

- 链路复位:通过RST#信号的触发,所有编解码器都返回到其上电状态。

- 编解码器复位:由软件发出指令,将特定的编解码器重置回其默认状态。

在以下三种事件之后,需要进行初始化序列:

- 链路复位

- 编解码器复位

- 编解码器更改其电源状态(例如,热插拔编解码器到HDA系统)。 在上述事件发生后,需要进行初始化以确保系统的正确运行。

7.3.1. 链路复位

链路复位可能由以下3个事件引起:

- HDA控制器以任何原因(上电或PCI复位)断言RST#信号。

- 软件通过HDA控制器的全局控制寄存器(GCR)中的'CRST'位发起链路复位。

- 软件启动电源管理序列。 图13显示了“链路复位”的时序,包括“进入”序列(1-5)和“退出”序列(6-9)。

在链路复位期间,HDA控制器和编解码器将返回到其上电状态,确保系统处于可靠的初始状态。

进入“链路复位”状态:

软件将一个0写入HDA控制器的全局控制寄存器的“CRST”位,以启动链路复位。

当控制器完成当前帧时,它不会在帧结束时发出正常的8位帧SYNC信号。

控制器将SYNC和所有SDO信号拉低。编解码器也将SDI信号拉低。

控制器将RST#信号拉低,并进入“链路复位”状态。

所有由控制器和编解码器驱动的链路信号应该通过内部上拉低电阻器处于三态状态。

退出“链路复位”状态:

如果由于任何原因重新启动BCLK(例如编解码器唤醒事件、电源管理等)。

软件负责在至少经过100微秒的BCLK运行时间后将RST#解除断开(这100微秒提供了编解码器PLL稳定的时间)。

在RST#解除断开后至少经过4个BCLK周期,控制器开始发出正常的帧SYNC信号。

当编解码器将其SDI驱动为请求初始化序列时(当SDI在帧SYNC的最后一位驱动为高电平时,表示编解码器请求初始化序列)。

7.3.2. 编解码器复位

“编解码器复位”是通过编解码器的RESET命令动词发起的。它导致目标编解码器被重置为默认状态。在目标编解码器完成复位操作后,将请求执行初始化序列。

编解码器初始化序列”是在以下步骤中进行的:

- 1 编解码器在SYNC的最后一位上将SDI置高,以请求从控制器获得编解码器地址(CAD)。

- 2 编解码器将在此时段内停止驱动SDI,即开始执行回转过程。

- 3 4 5 6 控制器驱动SDI为编解码器分配一个CAD。

- 7 控制器在分配了CAD后释放SDI。

- 8 进入正常操作状态。

7.4. Verb和响应格式

Verb ID是用于指示操作类型的标识符。它用于描述在音频系统中执行的不同操作。不同的Verb ID对应不同的功能或命令,例如读取或写入寄存器、请求设备初始化等。

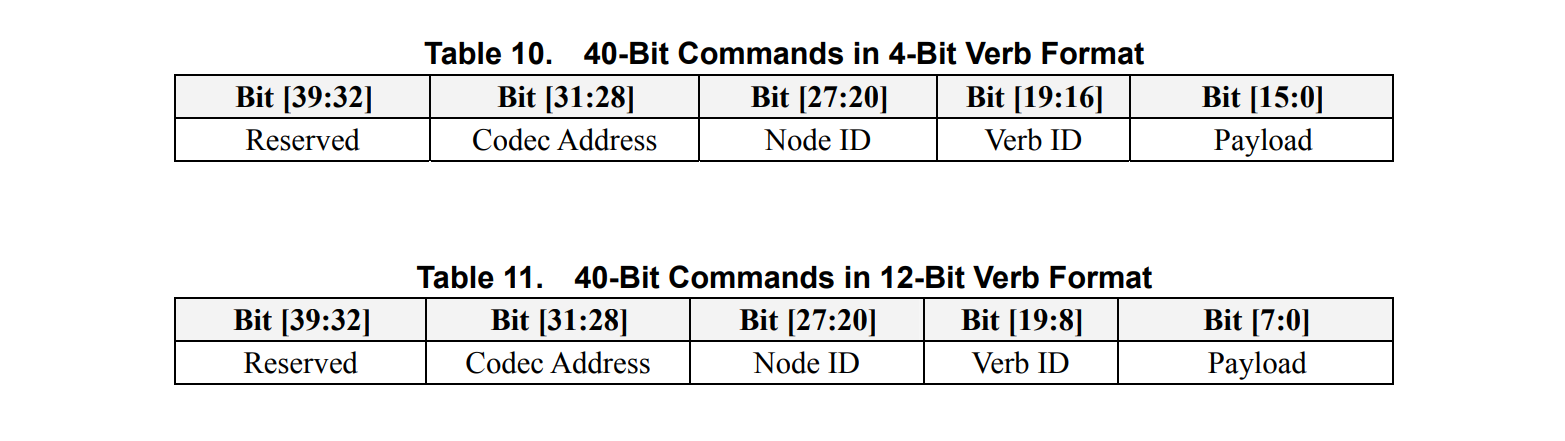

在表10中,位[27:20]表示Verb ID。由于这是一个4位字段,因此可以有16种不同的Verb ID,从0000(0)到1111(15)。每个Verb ID对应着不同的音频操作。例如,Verb ID为0000(0)可能代表一个读取操作,Verb ID为0001(1)可能代表一个写入操作,而Verb ID为1111(15)可能代表设备初始化请求。

通过正确的Verb ID,控制器和设备之间可以进行正确的通信,并执行所需的操作。

7.4.1. 命令Verb格式

有两种类型的Verb;一种是带有4位标识符(4位Verb),并带有16位数据,另一种是带有12位标识符(12位Verb),并带有8位数据。表10显示了从控制器发送到编解码器的命令流的4位Verb结构。表11是获取和控制编解码器参数的12位Verb结构。

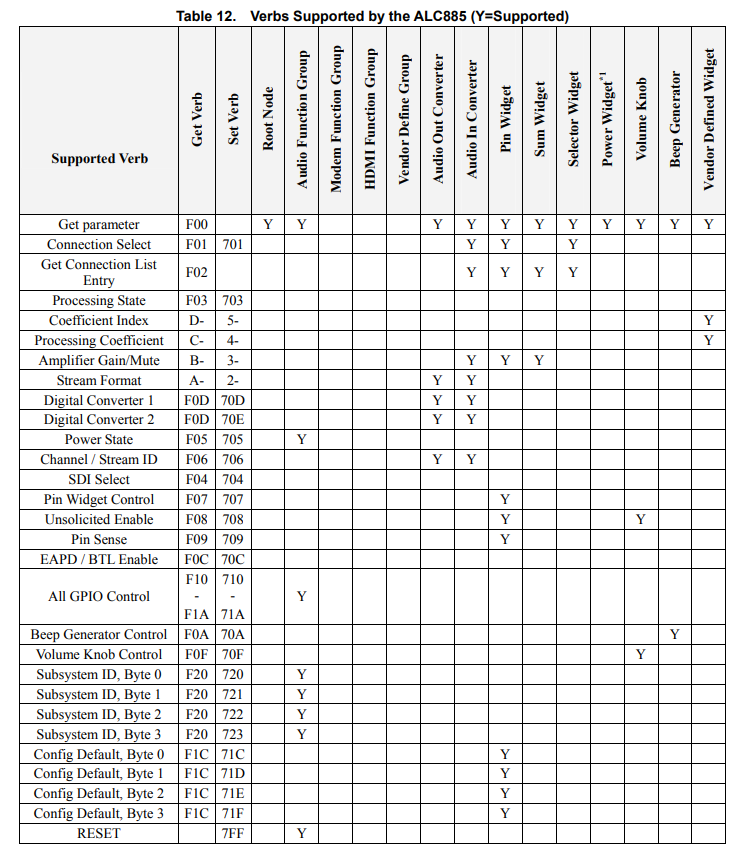

7.4.1.1 Verbs Supported by the ALC885 (Y=Supported)

在表12中列出了ALC885音频编解码器支持的不同Verb(操作)及其是否被支持的信息。以下是各个Verb的解释:

这些是ALC885音频编解码器支持的Verb类型:

- Get parameter: 获取参数,用于请求获取特定参数的值。

- Connection Select: 连接选择,用于选择特定的连接。

- Get Connection List Entry: 获取连接列表项,用于请求获取连接列表中的特定项。

- Processing State: 处理状态,用于表示处理状态。

- Coefficient Index: 系数索引,用于表示系数的索引值。

- Processing Coefficient: 处理系数,用于表示处理的系数值。

- Amplifier Gain/Mute: 放大器增益/静音,用于表示放大器的增益或静音状态。

- Stream Format: 流格式,用于表示数据流的格式。

- Digital Converter 1: 数字转换器 1,用于表示数字转换器的相关参数。

- Digital Converter 2: 数字转换器 2,用于表示数字转换器的相关参数。

- Power State: 电源状态,用于表示组件的电源状态。

- Channel / Stream ID: 通道/流ID,用于表示通道或数据流的ID。

- SDI Select: SDI选择,用于选择特定的SDI信号。

- Pin Widget Control: 引脚组件控制,用于控制引脚组件的相关功能。

- Unsolicited Enable: 未请求启用,用于启用未请求的事件通知。

- Pin Sense: 引脚感知,用于表示引脚的感知状态。

- EAPD / BTL Enable: EAPD/BTL启用,用于启用EAPD或BTL功能。

- All GPIO Control: 所有GPIO控制,用于控制所有GPIO的状态。

- Beep Generator Control: 蜂鸣器生成器控制,用于控制蜂鸣器生成器的状态。

- Volume Knob Control: 音量旋钮控制,用于控制音量旋钮的状态。

- Subsystem ID, Byte 0: 子系统ID,字节0,用于表示子系统的ID信息。

- Subsystem ID, Byte 1: 子系统ID,字节1,用于表示子系统的ID信息。

- Subsystem ID, Byte 2: 子系统ID,字节2,用于表示子系统的ID信息。

- Subsystem ID, Byte 3: 子系统ID,字节3,用于表示子系统的ID信息。

- Config Default, Byte 0: 默认配置,字节0,用于表示默认配置的信息。

- Config Default, Byte 1: 默认配置,字节1,用于表示默认配置的信息。

- Config Default, Byte 2: 默认配置,字节2,用于表示默认配置的信息。

- Config Default, Byte 3: 默认配置,字节3,用于表示默认配置的信息。

- RESET: 重置,用于重置特定组件或整个系统。

这些是ALC885音频编解码器支持的部分Widget类型:

- Get Verb: 获取Verb,用于请求获取特定Verb的值。

- Set Verb: 设置Verb,用于设置特定Verb的值。

- Root Node: 根节点,代表音频链路的根节点。

- Audio Function Group: 音频功能组,用于表示音频功能组件。

- Modem Function Group: 调制解调器功能组,用于表示调制解调器功能组件。

- HDMI Function Group: HDMI功能组,用于表示HDMI功能组件。

- Vendor Define Group: 厂商定义组,用于表示厂商定义的功能组件。

- Audio Out Converter: 音频输出转换器,用于表示音频输出转换器组件。

- Audio In Converter: 音频输入转换器,用于表示音频输入转换器组件。

- Pin Widget: 引脚组件,用于表示引脚组件。

- Sum Widget: 汇总组件,用于表示汇总组件。

- Selector Widget: 选择器组件,用于表示选择器组件。

- Power Widget: 电源组件,用于表示电源组件。

- Volume Knob: 音量旋钮,用于表示音量旋钮组件。

- Beep Generator: 蜂鸣器生成器,用于表示蜂鸣器生成器组件。

- Vendor Defined Widget: 厂商定义的组件,用于表示厂商定义的组件。

表中的Y表示支持该Verb,而“-”表示不支持。控制器通过使用这些Verb来与ALC885音频编解码器进行通信,并对其进行配置和控制。

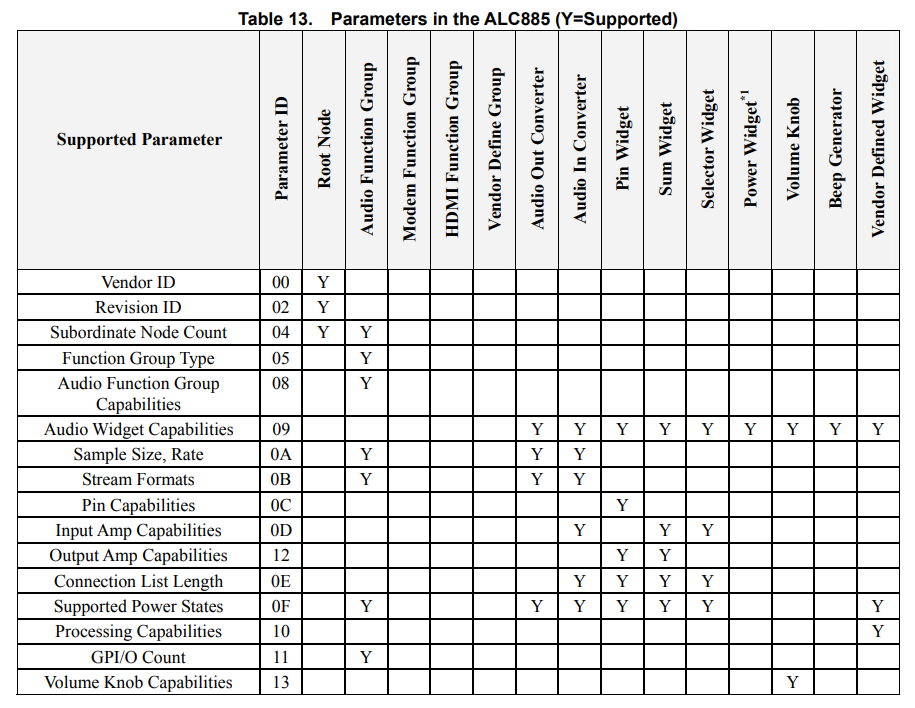

7.4.1.2 Parameters in the ALC885 (Y=Supported)

这些是ALC885音频编解码器支持的参数:

- Vendor ID - 厂商ID:标识音频编解码器的制造商,通常是一个唯一的代码。它可以用于识别设备的制造商。

- Revision ID - 修订ID:标识音频编解码器的硬件或固件版本,用于区分不同版本的设备。

- Subordinate Node Count - 下级节点计数:指示一个功能组拥有的下级节点(例如子功能组、子设备等)的数量。

- Function Group Type - 功能组类型:表示功能组的类型,用于区分不同类型的功能组。

- Audio Function Group Capabilities - 音频功能组能力:描述音频功能组支持的功能和特性。

- Audio Widget Capabilities - 音频组件能力:描述音频组件(如输入转换器、输出转换器等)支持的功能和特性。

- Sample Size, Rate - 采样大小、速率:指示音频组件支持的采样位数和采样率。

- Stream Formats - 流格式:指示音频组件支持的数据流格式,包括编码方式和通道数等。

- Pin Capabilities - 引脚能力:描述音频编解码器的引脚组件(输入和输出)的功能和特性。

- Input Amp Capabilities - 输入放大器能力:描述音频输入转换器的放大器功能和特性。

- Output Amp Capabilities - 输出放大器能力:描述音频输出转换器的放大器功能和特性。

- Connection List Length - 连接列表长度:指示音频组件支持的连接列表长度,用于描述与其他组件的连接关系。

- Supported Power States - 支持的电源状态:描述音频组件支持的不同电源状态,例如开机、待机、关机等。

- Processing Capabilities - 处理能力:描述音频组件支持的音频处理功能和特性。

- GPI/O Count - 通用输入/输出(GPI/O)计数:指示音频编解码器支持的通用输入/输出端口数量。

- Volume Knob Capabilities - 音量旋钮能力:描述音量旋钮组件的功能和特性,用于调节音频输出的音量大小。

这些是ALC885音频编解码器支持的Widget类型:

- Parameter ID - 参数ID:标识音频编解码器内部的各种参数,用于获取或设置特定的配置项。

- Root Node - 根节点:音频编解码器的根节点,用于标识功能组的顶级节点。

- Audio Function Group - 音频功能组:表示音频功能的一个组,包含多个音频组件。

- Modem Function Group - 调制解调器功能组:表示调制解调器功能的一个组,包含多个调制解调器组件。

- HDMI Function Group - HDMI功能组:表示HDMI功能的一个组,包含多个HDMI组件。

- Vendor Define Group - 厂商定义组:由制造商定义的特定功能组,用于实现自定义功能。

- Audio Out Converter - 音频输出转换器:用于将音频数据转换为模拟输出信号的组件。

- Audio In Converter - 音频输入转换器:用于将模拟音频信号转换为数字音频数据的组件。

- Pin Widget - 引脚组件:音频编解码器的引脚组件,用于连接不同音频组件。

- Sum Widget - 汇总组件:将多个输入音频流混合为单个输出音频流的组件。

- Selector Widget - 选择组件:用于在多个输入音频流中选择一个作为输出音频流的组件。

- Power Widget1 - 电源组件1:控制音频组件的电源状态的组件。

- Volume Knob - 音量旋钮:用于调节音频输出的音量大小的组件。

- Beep Generator - 蜂鸣器发生器:产生蜂鸣音的组件。

- Vendor Defined Widget - 厂商定义组件:由制造商定义的特定组件,用于实现自定义功能。

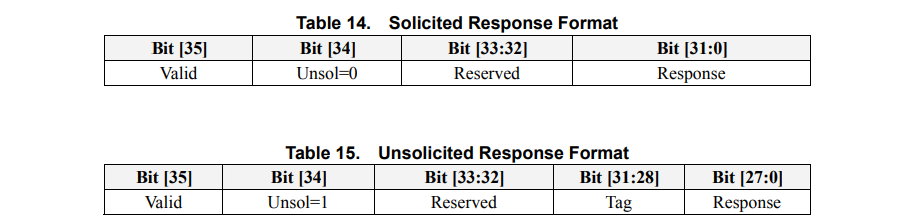

7.4.2. 回应格式

从编解码器到控制器,有两种类型的回应。被请求回应是编解码器对当前命令动词的回应。编解码器将在下一帧中发送被请求回应数据,而不考虑Set(写入)或Get(读取)命令。32位回应由软件解释,对于控制器而言是不透明的。

主动回应是由编解码器独立于软件请求发送的。插孔检测或GPI状态信息可以主动传递给控制器,并由软件进行解释。Bit [31:28]中的“Tag”用于标识主动回应事件。该标记在HDA规范中未定义。

注意:在链路协议中,回应流是36位宽。回应被放置在较低的32位字段中。第35位是一个“有效”位,用于指示回应已经“就绪”。第34位被设置为表示已发送未被请求的回应。

7.5. 电源管理

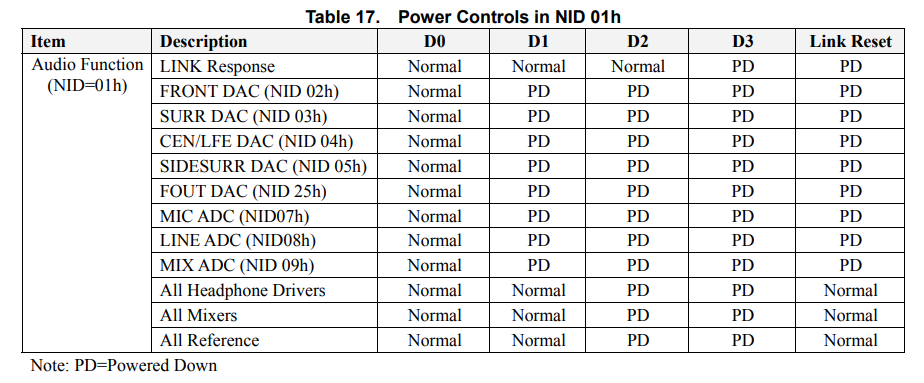

ALC885在低功耗模式下不支持唤醒事件。所有组件的电源管理状态变化都由软件控制。表16显示了系统电源状态的定义。 在ALC885中,所有组件,包括输出/输入转换器,都支持电源控制。软件可以根据系统配置设置各种电源状态。 表17显示了支持电源管理的节点。为了简化电源控制,软件可以通过音频功能(NID=01h)来配置整个编解码器的电源状态。输出转换器(DACs)和输入转换器(ADCs)没有独立的电源控制,因此无法提供精细的电源控制。

表16. 系统电源状态定义

| 电源状态 | 描述 |

|---|---|

| D0 | 所有电源开启。各个DAC和ADC可以根据需要开启或关闭电源。 |

| D1 | 所有放大器和转换器(DAC和ADC)被关闭电源。状态保持,模拟参考电压保持开启。 |

| D2 | 所有放大器和转换器(DAC和ADC)被关闭电源。状态保持,但模拟参考电压关闭(D1状态加上关闭模拟参考电压)。 |

| D3 (Hot) | 电源仍供应。编解码器停止内部时钟。状态保持。 |

| D3 (Cold) | 所有电源被切断。状态丢失。 |

表17. NID 01h中的电源控制

| 节点 | 描述 | D0 | D1 | D2 | D3 (Link Reset) |

|---|---|---|---|---|---|

| LINK Response | 连接响应 | 正常 | 正常 | 正常 | 关闭电源 (PD) |

| FRONT DAC (NID 02h) | 前声道DAC (NID 02h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| SURR DAC (NID 03h) | 环绕声DAC (NID 03h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| CEN/LFE DAC (NID 04h) | 中置/低频效果DAC (NID 04h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| SIDESURR DAC (NID 05h) | 边置环绕声DAC (NID 05h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| FOUT DAC (NID 25h) | 输出DAC (NID 25h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| MIC ADC (NID 07h) | 麦克风ADC (NID 07h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| LINE ADC (NID 08h) | 线路ADC (NID 08h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| MIX ADC (NID 09h) | 混音ADC (NID 09h) | 正常 | 关闭电源 (PD) | 关闭电源 (PD) | 关闭电源 (PD) |

| All Headphone Drivers | 所有耳机驱动器 | 正常 | 正常 | 关闭电源 (PD) | 正常 |

| All Mixers | 所有混音器 | 正常 | 正常 | 关闭电源 (PD) | 正常 |

| Audio Function (NID=01h) | 音频功能 (NID=01h) | 正常 | 正常 | 关闭电源 (PD) | 正常 |

| All Reference | 所有参考电源 | 正常 | 正常 | 关闭电源 (PD) | 正常 |

注:

- D0:所有电源开启,正常工作状态。

- D1:关闭所有放大器和转换器(DAC和ADC),维持状态,模拟参考电压保持开启。

- D2:关闭所有放大器和转换器(DAC和ADC),维持状态,但模拟参考电压关闭。

- D3 (Link Reset):关闭所有电源,状态丢失。

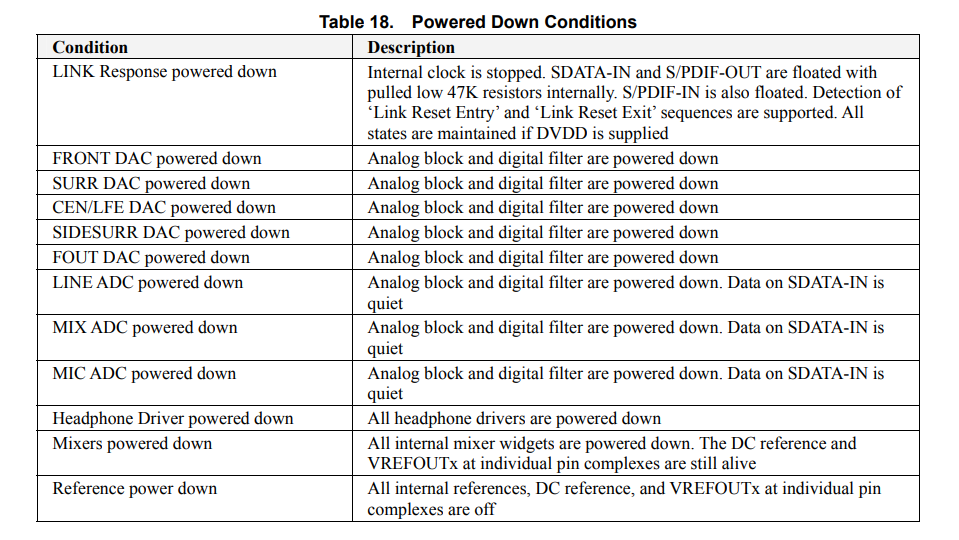

表18. 关闭电源的条件

| 条件 | 描述 |

|---|---|

| LINK Response电源关闭 | 内部时钟停止。SDATA-IN和S/PDIF-OUT通过内部拉低47K电阻浮置。S/PDIF-IN也被浮置。仍支持“Link Reset Entry”和“Link Reset Exit”序列的检测。如果提供DVDD,则所有状态将保持。 |

| FRONT DAC电源关闭 | 模拟块和数字滤波器被关闭电源。 |

| SURR DAC电源关闭 | 模拟块和数字滤波器被关闭电源。 |

| CEN/LFE DAC电源关闭 | 模拟块和数字滤波器被关闭电源。 |

| SIDESURR DAC电源关闭 | 模拟块和数字滤波器被关闭电源。 |

| FOUT DAC电源关闭 | 模拟块和数字滤波器被关闭电源。 |

| LINE ADC电源关闭 | 模拟块和数字滤波器被关闭电源。SDATA-IN上的数据静默。 |

| MIX ADC电源关闭 | 模拟块和数字滤波器被关闭电源。SDATA-IN上的数据静默。 |

| MIC ADC电源关闭 | 模拟块和数字滤波器被关闭电源。SDATA-IN上的数据静默。 |

| 耳机放大器电源关闭 | 所有耳机放大器被关闭电源。 |

| 混音器电源关闭 | 所有内部混音器部件被关闭电源。各个引脚复合体的DC参考和VREFOUTx仍然保持。 |

| 参考电源关闭 | 所有内部参考、DC参考和各个引脚复合体上的VREFOUTx被关闭电源。 |

8. 支持的Verbs和Parameters

本节描述了ALC885中各种部件支持的Verbs和Parameters。如果所寻址的部件不支持某个Verb,则它将回复32位的“0”。

8.1. Verb - 获取参数 (Verb ID=F00h)

'获取参数' Verb 用于获取HDA编解码器的系统信息和功能能力。所有参数都是只读的。每个部件都定义了总共15个ID参数。一些参数仅在特定部件中支持。有关支持的参数的详细信息,请参阅第7.4.1节“命令Verb格式”,第21页。